#### OBSERVATOIRE DE PARIS

### ÉCOLE DOCTORALE ASTRONOMIE ET ASTROPHYSIQUE D'ÎLE-DE-FRANCE

## $\begin{array}{c} {\rm Thesis} \\ {\bf ASTRONOMY~AND~ASTROPHYSICS} \\ {\rm Instrumentation} \end{array}$

#### Shan Mignot

Towards a demonstrator for autonomous object detection on board Gaia

(Vers un demonstrateur pour la détection autonome des objets à bord de Gaia)

Thesis directed by Jean Lacroix then Albert Bijaoui

Presented on January 10th 2008 to a jury composed of:

| Ana Gómez          | GÉPI - Observatoire de Paris               | President |

|--------------------|--------------------------------------------|-----------|

| Bertrand Granado   | ETIS - ENSEA                               | Reviewer  |

| Michael Perryman   | ESTEC - Agence Spatiale Européenne         | Reviewer  |

| Daniel Gaffé       | LEAT - Université de Nice Sophia-Antipolis | Examiner  |

| Michel Paindavoine | LE2I - Université de Bourgogne             | Examiner  |

| Albert Bijaoui     | Cassiopée - Observatoire de la Côte d'Azur | Director  |

| Gregory Flandin    | EADS Astrium SAS                           | Guest     |

| Jean Lacroix       | LPMA - Université Paris 6                  | Guest     |

| Gilles Moury       | Centre National d'Études Spatiales         | Guest     |

## Acknowledgements

The journey to the stars is a long one. If the poet may with one swift movement of his imagination sweep the reader off his feet to embark at their summons on a voyage to the blinking stars, for the multitude, the path remains undecipherable. Many an intriguing stratagems have been devised by generations of men yearning for such freedom and, alas, of those who have succeeded little remains but awe for their genius or for their folly. By no means do we hope to compare with them. Instead, with the sand at our feet to the stars above our heads, we venture to construct a ladder, grain per grain, and with infinite patience and method, eventually, step by step. May the readers forgive the means, overlook the ticking of the inflexible clock and bear with us long enough to either discard our laborious undertaking with evidence or to contribute their own grain... for such an endeavour cannot be a solitary one.

And, indeed, a solitary one it has not been. From the start, the buzz of the contradictors and of the collaborators was heard surrounding our molehill. Certainly, the improbable balance in which it now stands owes much to the varied views of the scientists, of the engineers, of the agencies as of industry. Pray, accept our gratitude for doubts, good counsels, militant beliefs, patient contributions, precise criticisms have shaped the edifice, sometimes like a wind bringing down feverish protrusions, sometimes like a lever. Of all, special praise must be given to my directors and my proofreaders, and among them to Philippe Laporte who has not only groped for viable solutions in the realm of hardware in our company, but has also bravely ventured in inspecting every single portion of this text where many dangers lay in hidding.

Family, friends and our sweetheart have also played a decisive role. Some with earthly, and others with not so earthly means. Let them not be forgotten, for if we have come within reach of the stars it is certainly because they have made us stand as on the shoulders of giants.

## Contents

| Fo       | orewo          | ord                           | xiii |

|----------|----------------|-------------------------------|------|

| Ι        | Int            | troduction                    | 1    |

| 1        | The            | e Gaia mission                | 3    |

|          | 1.1            | Introduction                  | 3    |

|          | 1.2            | Scientific return             | 5    |

|          | 1.3            | The satellite                 | 7    |

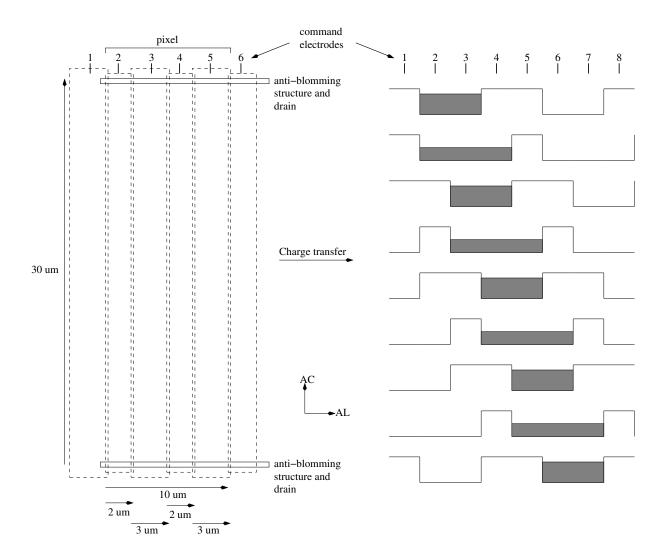

|          | 1.0            | 1.3.1 Measurement principle   | 7    |

|          |                | 1.3.2 Overview of operation   | 9    |

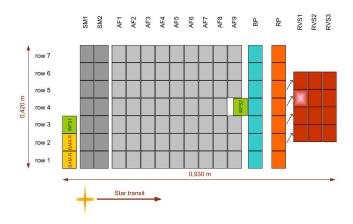

|          |                | 1.3.3 CCD technology          | 13   |

|          | 1.4            | Conclusion                    | 17   |

|          | 1.4            | Conclusion                    | 11   |

| <b>2</b> |                | -board processing             | 19   |

|          | 2.1            | Introduction                  | 19   |

|          | 2.2            | Functional needs              | 20   |

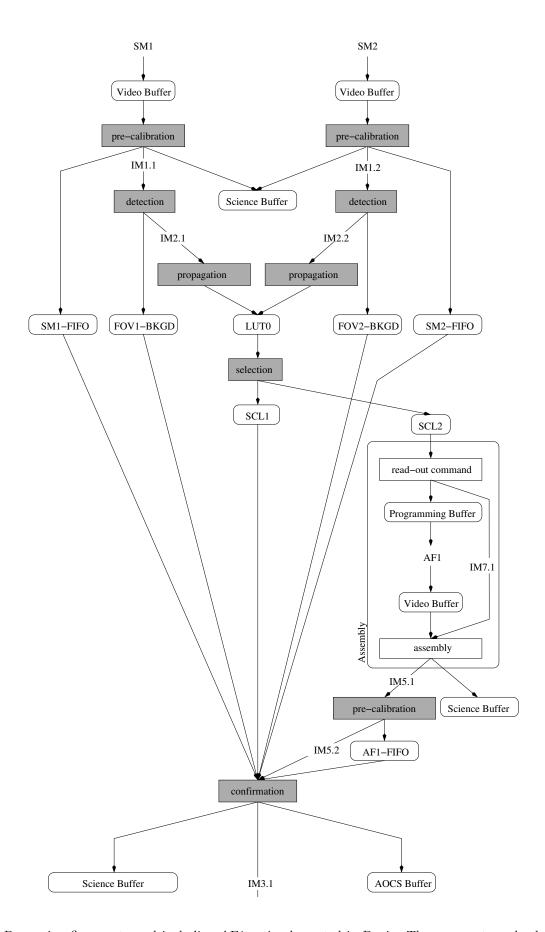

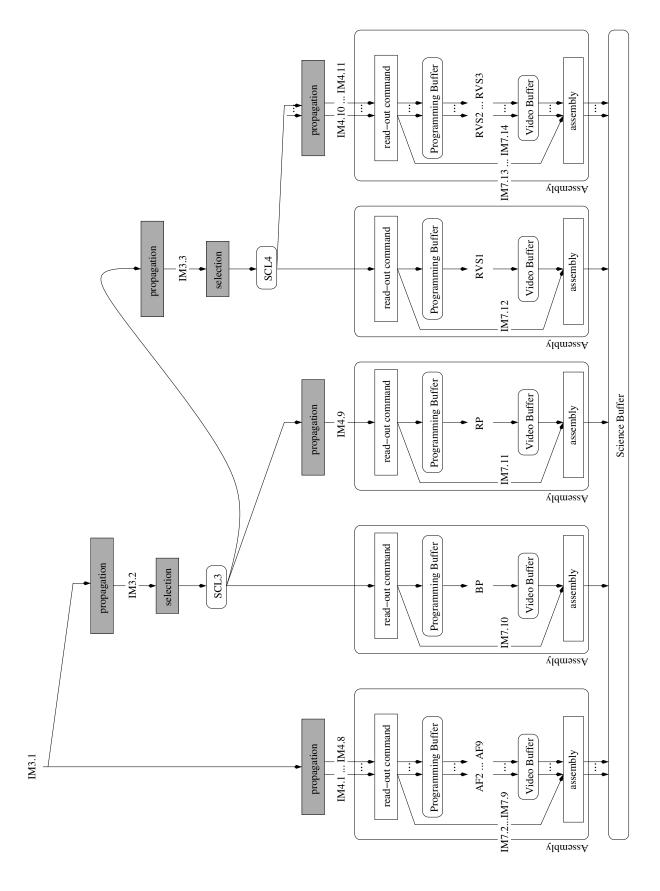

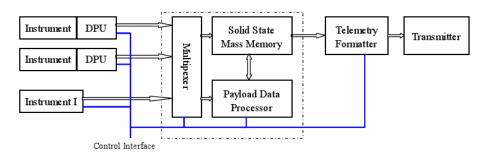

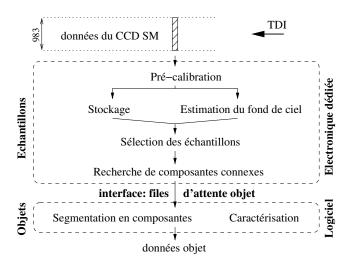

|          |                | 2.2.1 Processing flow         | 20   |

|          |                | 2.2.2 Specifications          | 21   |

|          |                | 2.2.3 Processing capabilities | 26   |

|          | 2.3            | Constraints                   | 26   |

|          |                | 2.3.1 Space                   | 26   |

|          |                | 2.3.2 Radiations              | 27   |

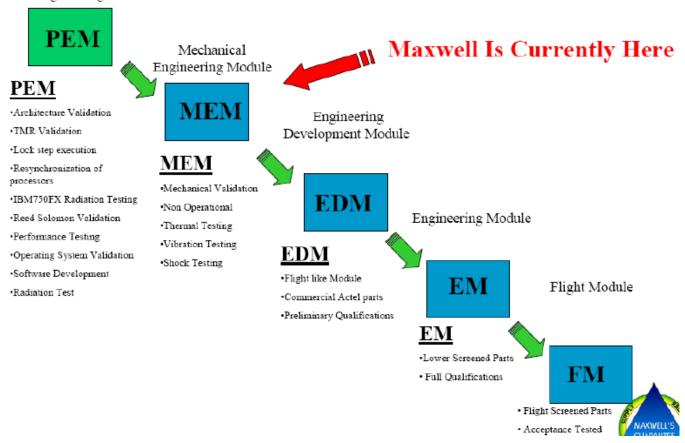

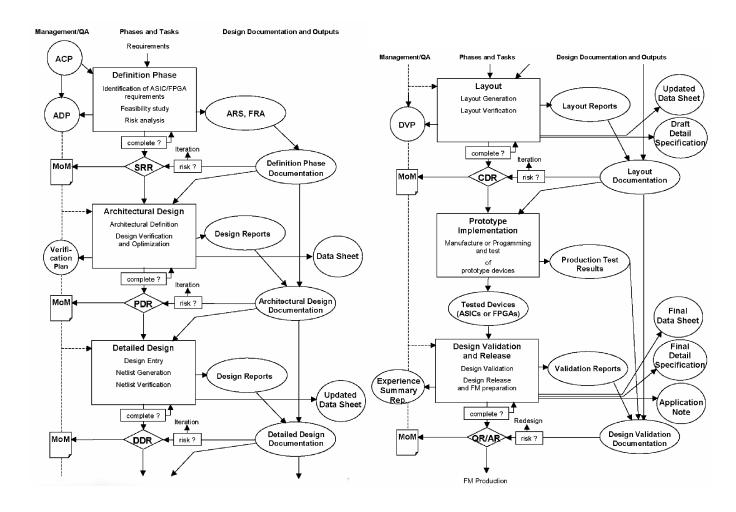

|          | 2.4            | Quality assurance             | 28   |

|          |                | 2.4.1 Component policy        | 28   |

|          |                | 2.4.2 Availability            | 29   |

|          |                | 2.4.3 Qualification           | 29   |

|          | 2.5            | Architecture                  | 30   |

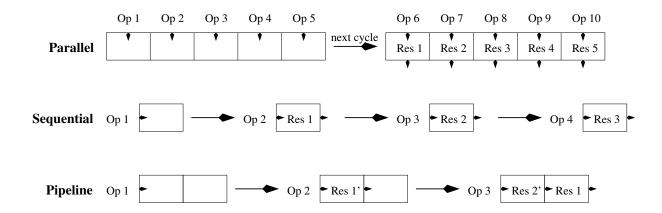

|          |                | 2.5.1 Paradigms               | 30   |

|          |                | 2.5.2 PDHS                    | 30   |

|          | 2.6            | Conclusion                    | 31   |

|          |                |                               |      |

| II       | <b>A</b>       | Algorithms                    | 33   |

| 3        | $\mathbf{Alg}$ | gorithmic framework           | 35   |

|          | 3.1            | Introduction                  | 35   |

|          |                | 3.1.1 A bit of history        | 35   |

|          |                | 3.1.2 Models                  | 36   |

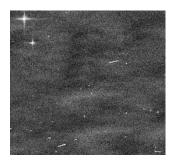

|          | 3.2            | Image model                   | 37   |

|          |                | 3.2.1 Acquisition             | 37   |

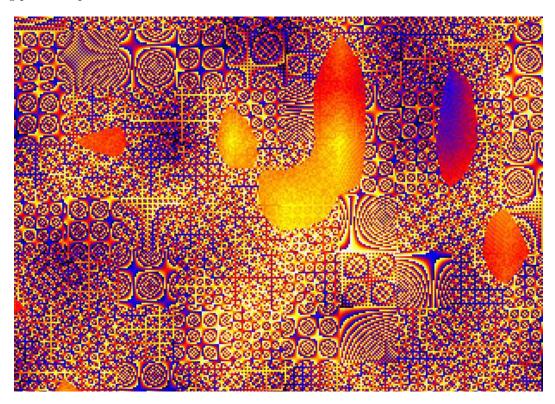

|          |                | 3.2.2 Simulation              | 39   |

|          | 3.3            | Needs                         | 40   |

|          | 3.4            | Approaches                    | 43   |

|          | J. 2           | 3.4.1 Transforms              | 43   |

|          |                | 3.4.2 Local analysis          | 44   |

|          |                | 3.4.3 Segmentation            | 44   |

|          | 3 5            | Processing flow               | 45   |

iv CONTENTS

|   |     | 3.5.1    | Software & hardware partition                                    | 45 |

|---|-----|----------|------------------------------------------------------------------|----|

|   |     | 3.5.2    | Overview                                                         | 46 |

|   | 3.6 | Conclus  | sion                                                             | 49 |

|   |     |          |                                                                  |    |

| 4 | Pre | -calibra |                                                                  | 53 |

|   | 4.1 | Introdu  | $\operatorname{ction}$                                           | 53 |

|   | 4.2 | Motivat  | tion                                                             | 54 |

|   |     | 4.2.1    | Effects                                                          | 54 |

|   |     | 4.2.2    | Policy                                                           | 54 |

|   | 4.3 | Algorith | hms t                                                            | 55 |

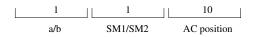

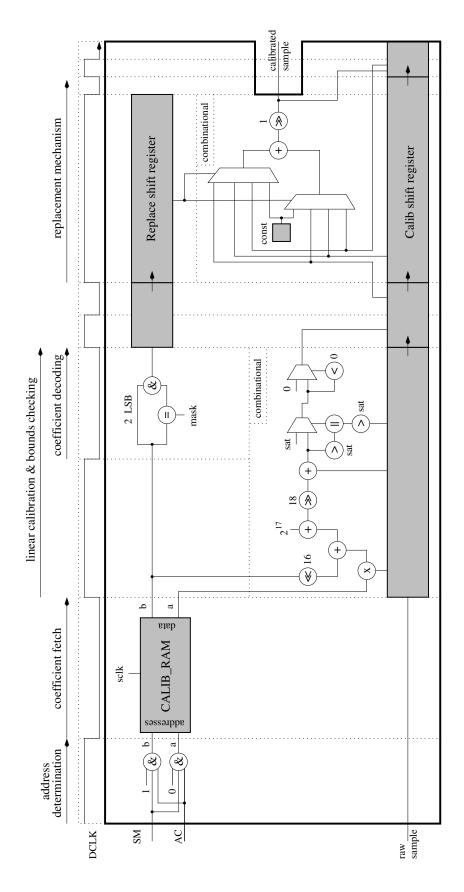

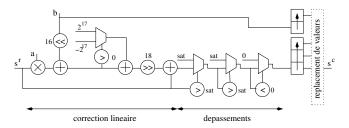

|   |     | 4.3.1    | Linear transform                                                 | 55 |

|   |     | 4.3.2    | Dead samples                                                     | 57 |

|   | 4.4 | Archite  | $\operatorname{cture} \ldots \ldots \ldots \ldots \ldots \ldots$ | 59 |

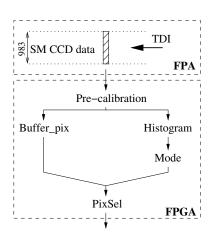

|   |     | 4.4.1    | Processing flow                                                  | 59 |

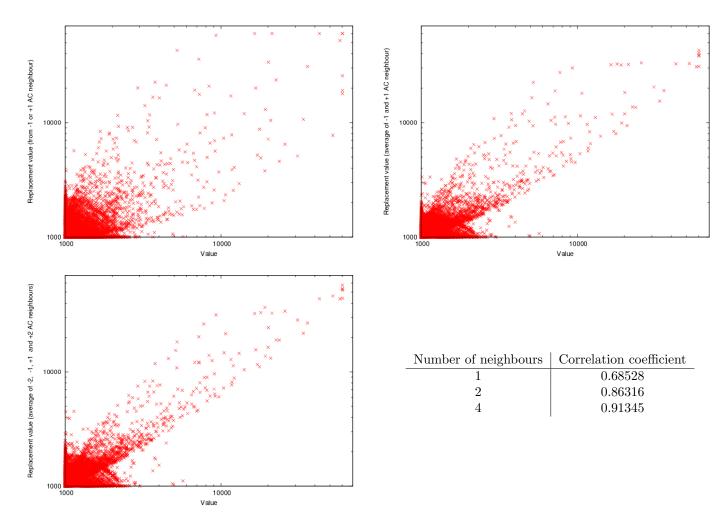

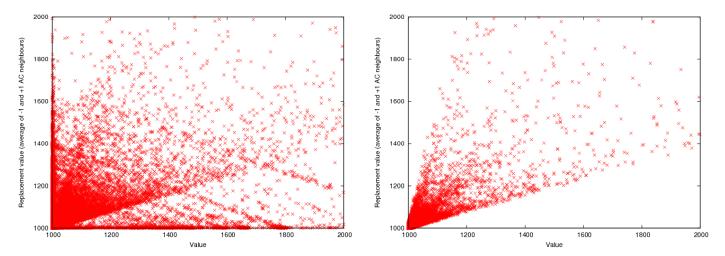

|   |     | 4.4.2    | Sample replacement                                               | 60 |

|   | 4.5 | Conclus  | sion                                                             | 60 |

|   |     |          |                                                                  |    |

| 5 | Bac | •        |                                                                  | 31 |

|   | 5.1 |          |                                                                  | 61 |

|   |     | 5.1.1    |                                                                  | 61 |

|   |     | 5.1.2    | Contributors                                                     | 62 |

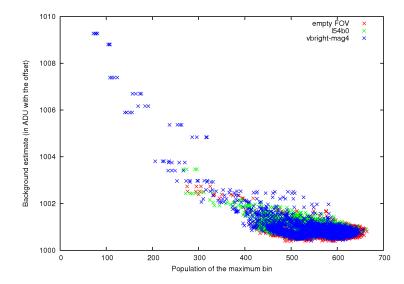

|   | 5.2 | Backgro  | ound statistic                                                   | 63 |

|   |     | 5.2.1    | Regional background                                              | 63 |

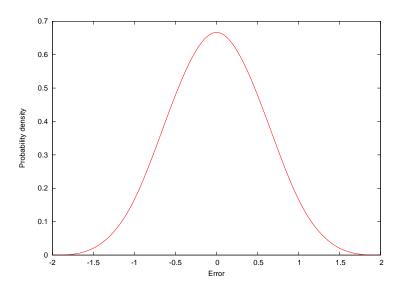

|   |     | 5.2.2    | Estimator                                                        | 64 |

|   |     | 5.2.3    | Replacement strategy                                             | 66 |

|   |     | 5.2.4    | Background map                                                   | 68 |

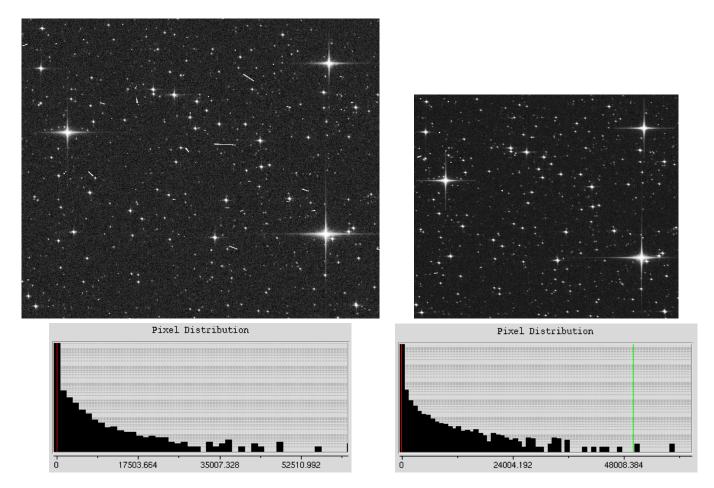

|   | 5.3 | Perform  | nances                                                           | 69 |

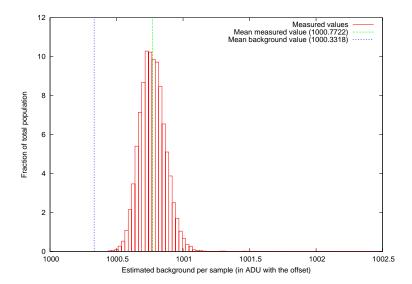

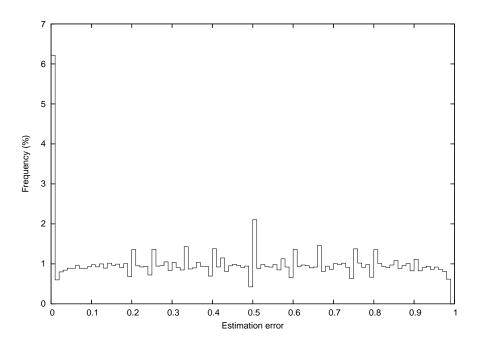

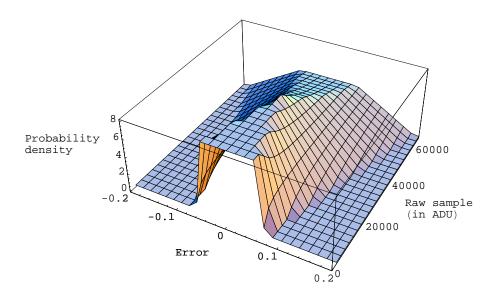

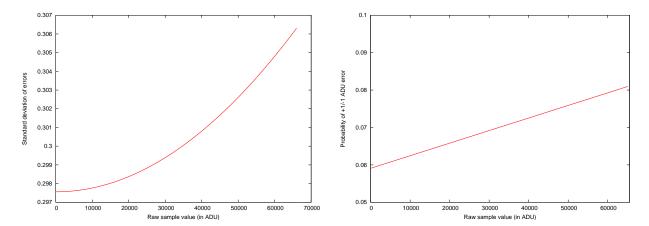

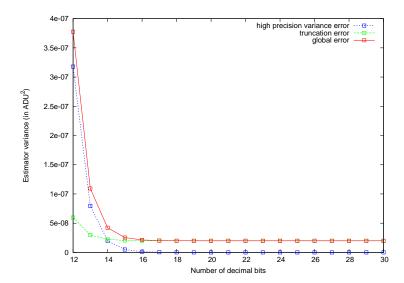

|   |     | 5.3.1    | Precision                                                        | 70 |

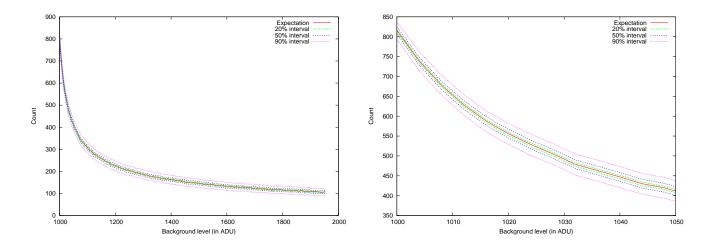

|   |     | 5.3.2    | Robustness                                                       | 70 |

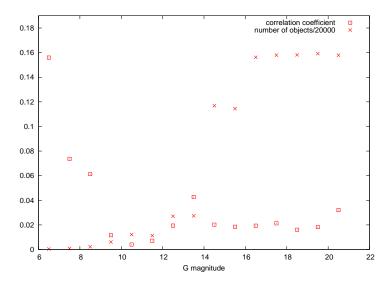

|   |     | 5.3.3    | Representativity                                                 | 71 |

|   | 5.4 | Algorith | hms                                                              | 72 |

|   |     | 5.4.1    | Histograms                                                       | 72 |

|   |     | 5.4.2    | Mode determination                                               | 73 |

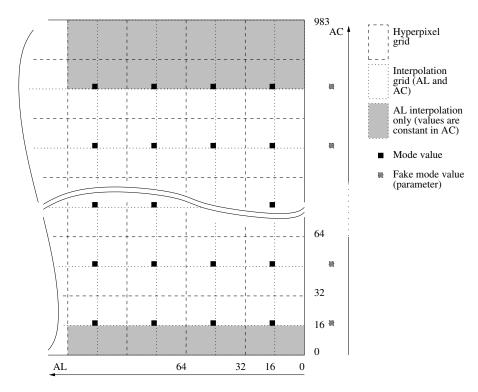

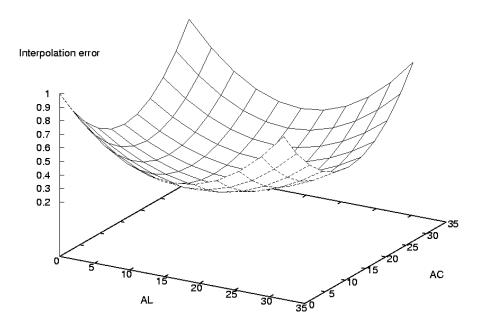

|   |     | 5.4.3    | Interpolation                                                    | 75 |

|   | 5.5 | Conclus  | sion                                                             | 76 |

|   |     |          |                                                                  |    |

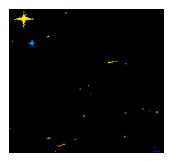

| 6 | Sim | ple obje | ect model                                                        | 77 |

|   | 6.1 | Introdu  | $\operatorname{ction}$                                           | 77 |

|   | 6.2 | SOM .    |                                                                  | 77 |

|   | 6.3 | -        |                                                                  | 78 |

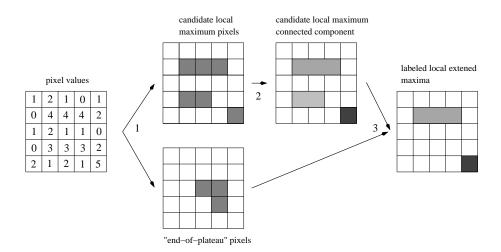

|   | 6.4 | Connec   | ted-component labelling                                          | 79 |

|   |     | 6.4.1    | Introduction                                                     | 79 |

|   |     | 6.4.2    | Definitions                                                      | 79 |

|   |     | 6.4.3    | Principle                                                        | 80 |

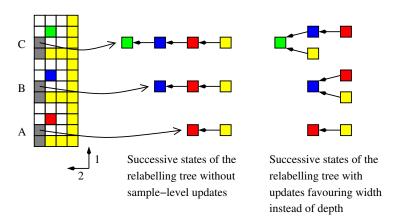

|   |     | 6.4.4    | Relabelling                                                      | 81 |

|   |     | 6.4.5    | Algorithm                                                        | 82 |

|   | 6.5 | SOM D    | escriptors                                                       | 87 |

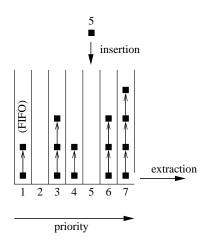

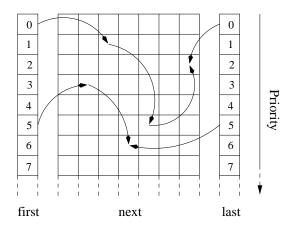

|   | 6.6 | Object   | queues                                                           | 87 |

|   | 6.7 | Conclus  | sion                                                             | 88 |

CONTENTS

| 7 | Fine | e object model                 | 89                |

|---|------|--------------------------------|-------------------|

|   | 7.1  | Introduction                   | 89                |

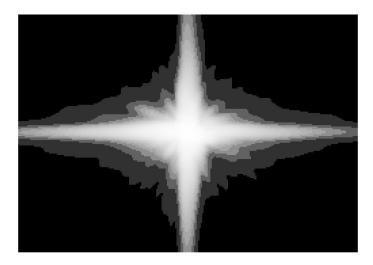

|   |      | 7.1.1 Structure                | 89                |

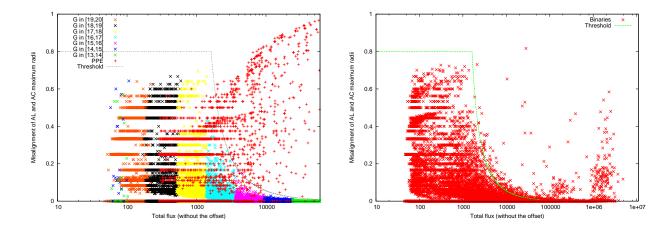

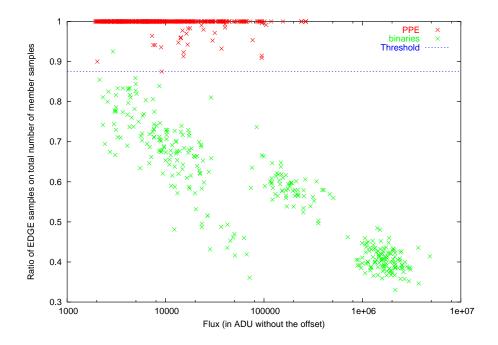

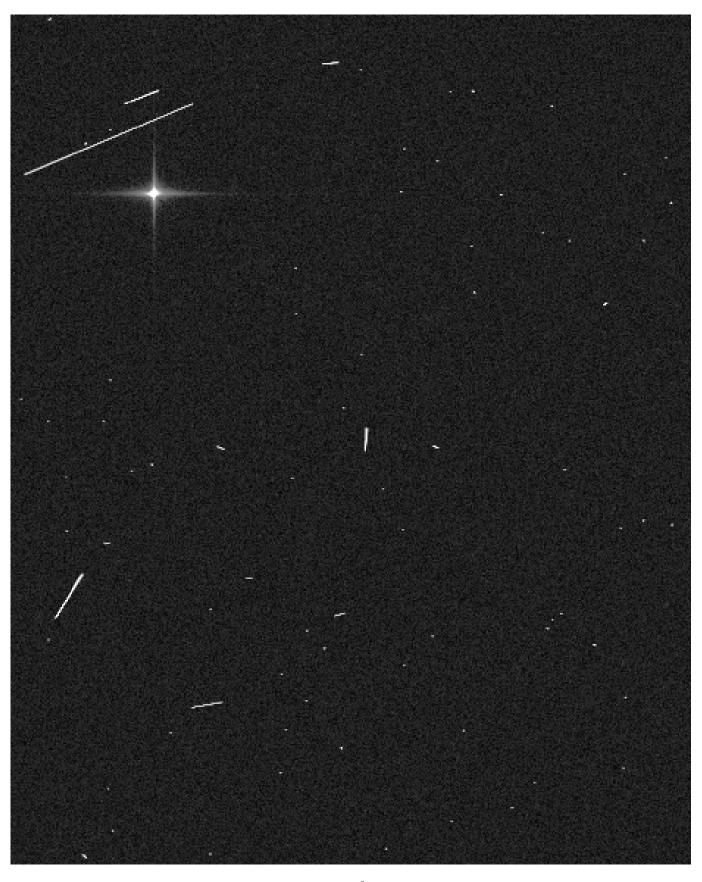

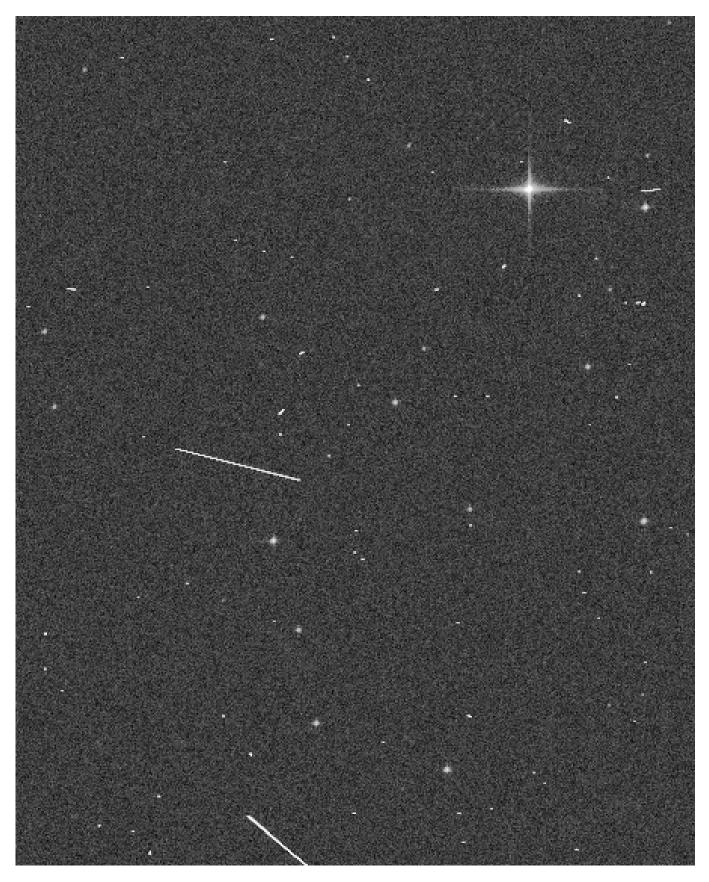

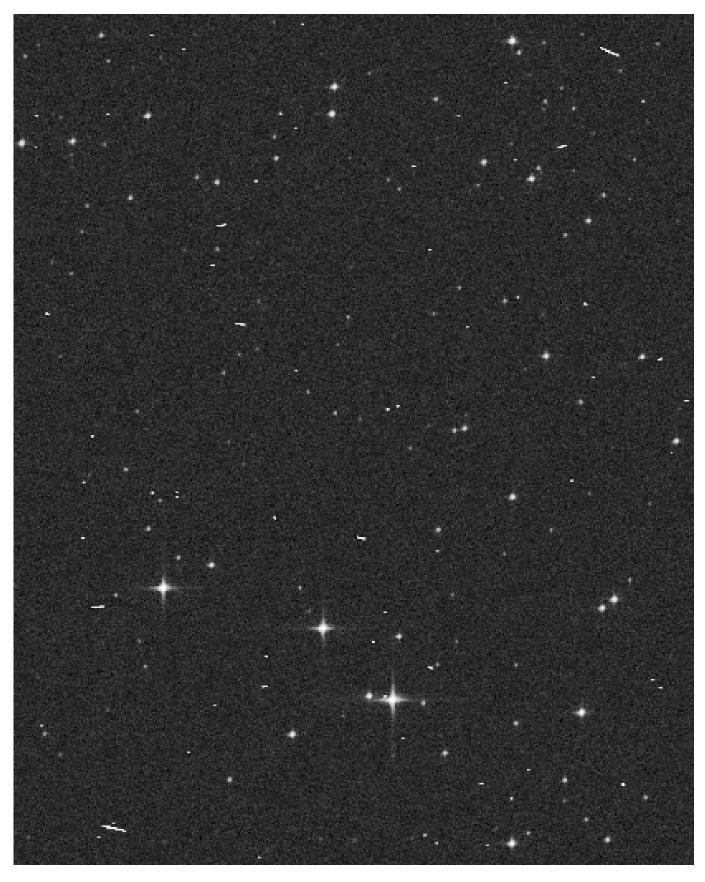

|   | 7.2  | Undesirable detections         | 91                |

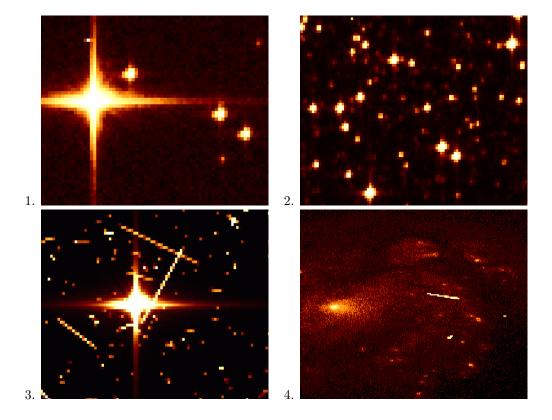

|   |      | 7.2.1 Faint objects            | 91                |

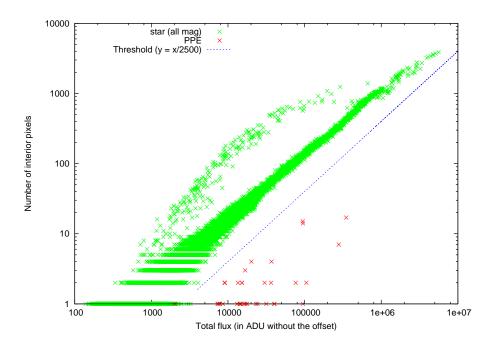

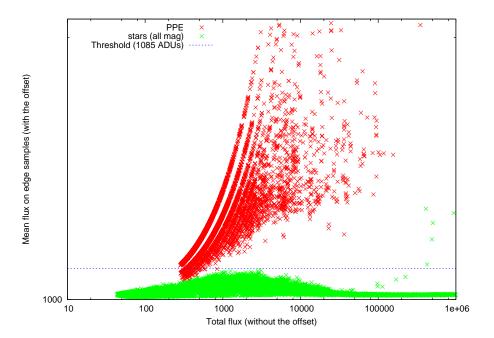

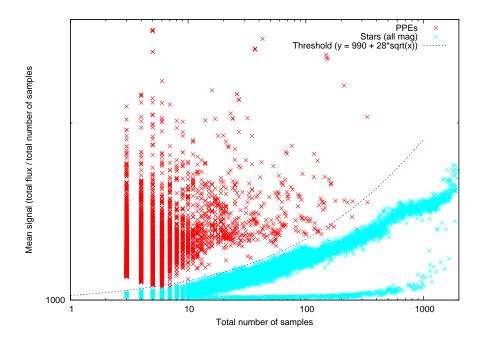

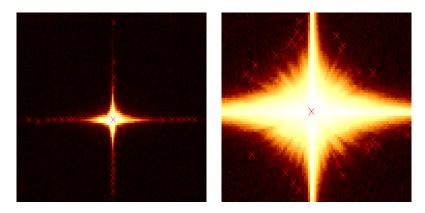

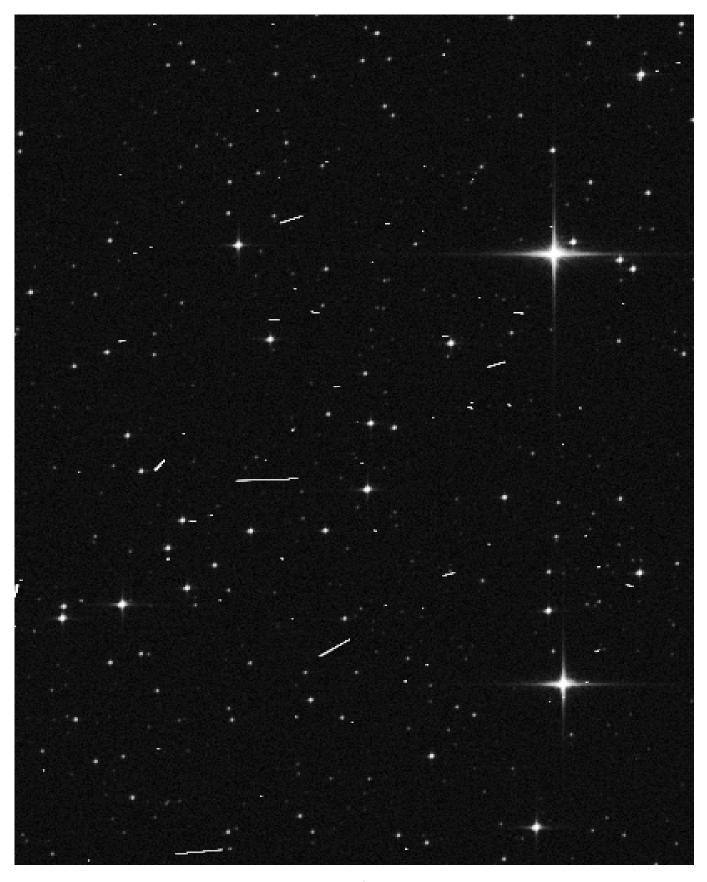

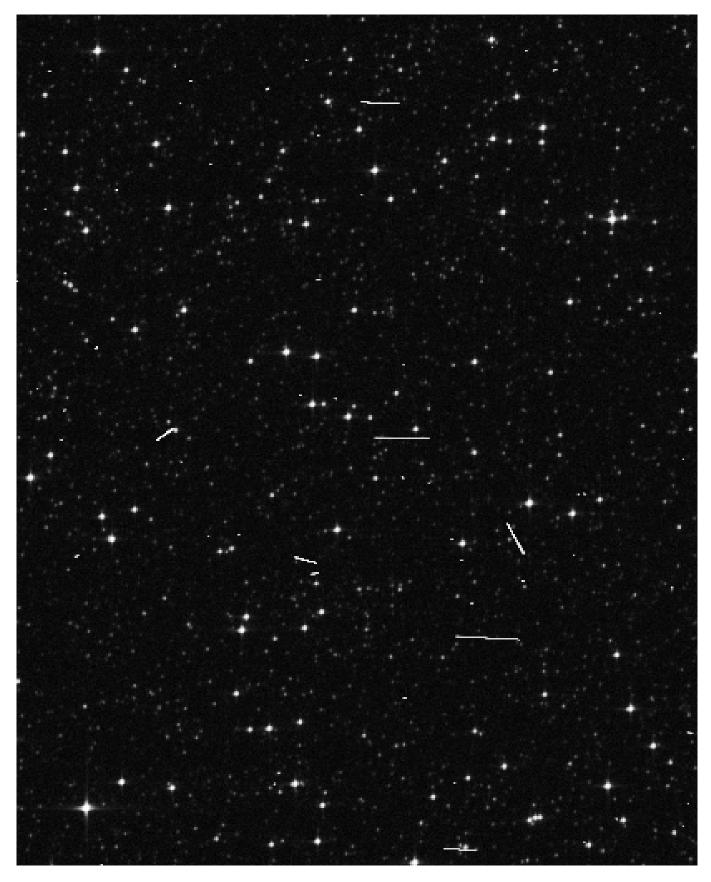

|   |      | 7.2.2 PPEs                     | 93                |

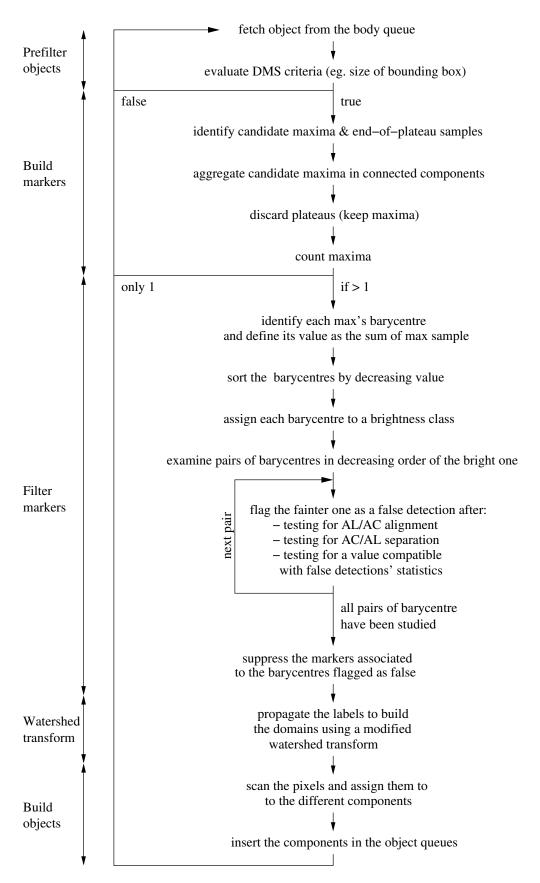

|   | 7.3  | Component segmentation         | 95                |

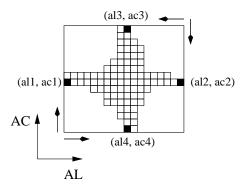

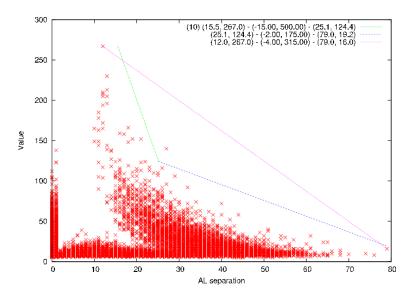

|   | 1.5  | -                              | 95<br>95          |

|   |      |                                |                   |

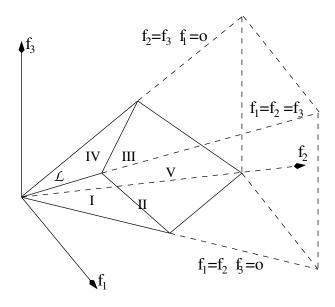

|   |      | 7.3.2 Segmentation paradigm    | 96                |

|   |      | 7.3.3 Markers                  | 98                |

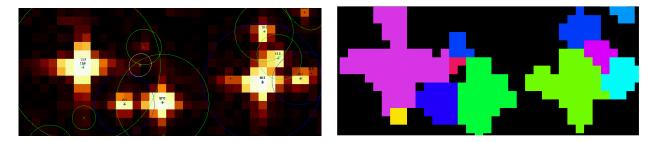

|   |      |                                | 102               |

|   | 7.4  | Measurements                   | 105               |

|   |      | 7.4.1 FOM descriptors          | 105               |

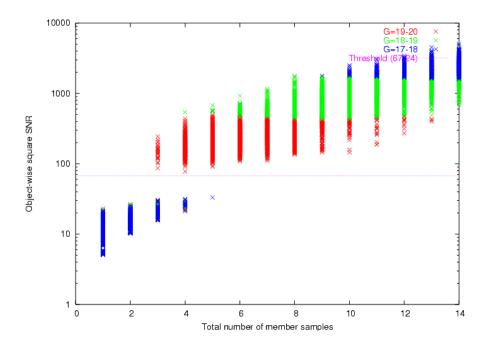

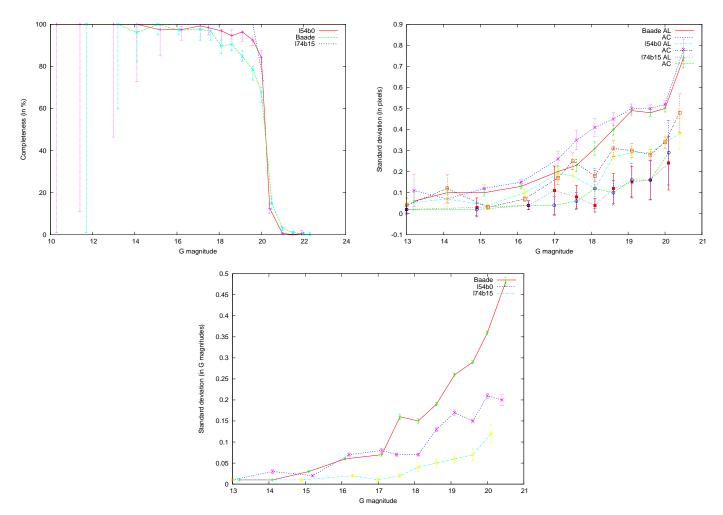

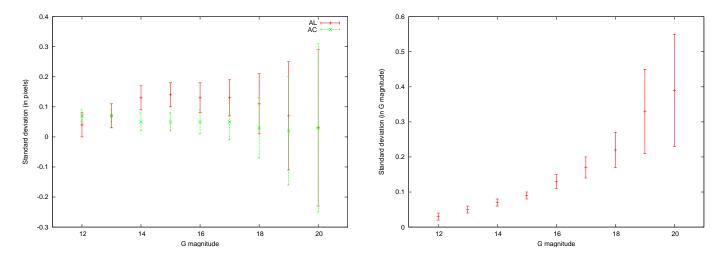

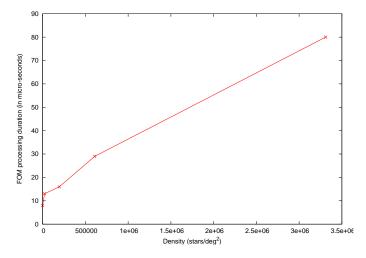

|   |      | 7.4.2 Performances             | 107               |

|   | 7.5  | Conclusion                     | 109               |

|   |      |                                |                   |

|   |      |                                |                   |

| Η | 1 1  | Implementation 1               | 111               |

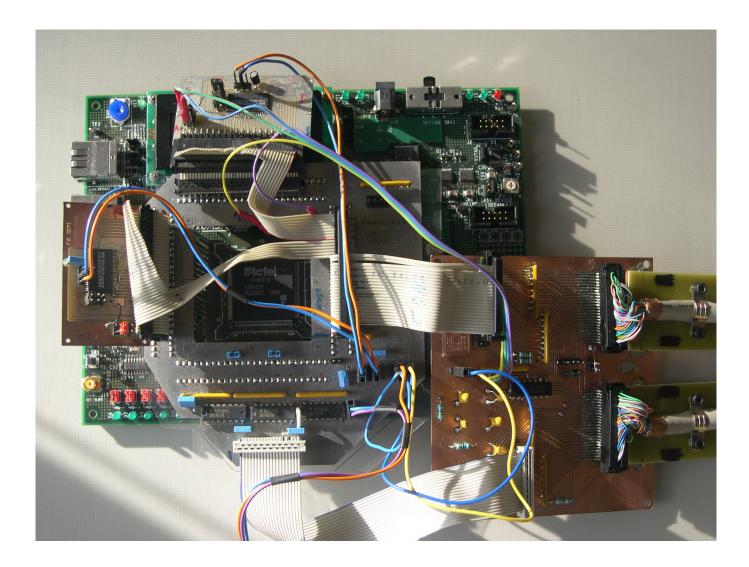

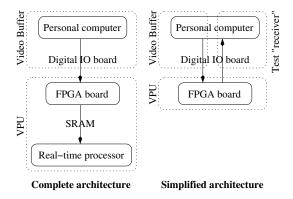

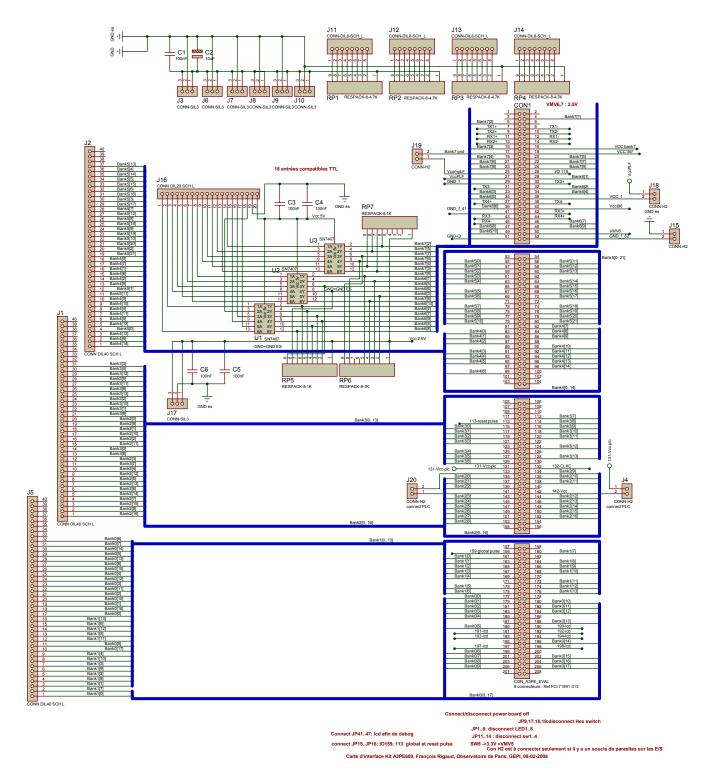

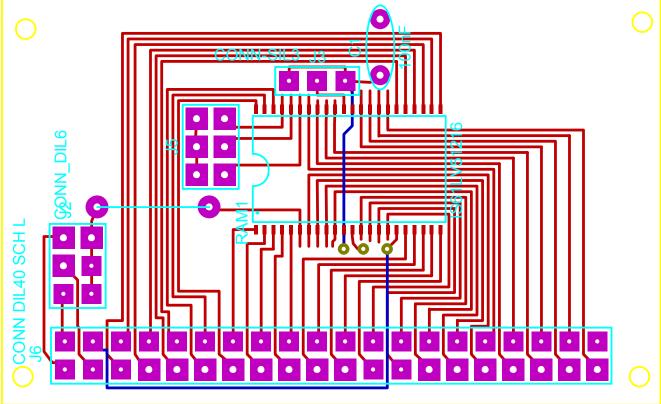

| 8 | Plat | $\mathbf{tform}$               | 113               |

|   | 8.1  |                                | 113               |

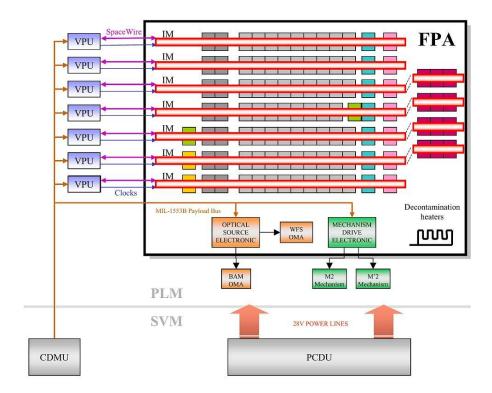

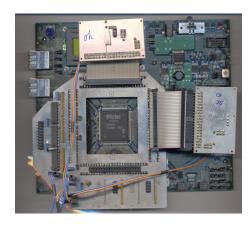

|   | 8.2  |                                | 114               |

|   | 0.2  | •                              | 114               |

|   |      |                                | 114               |

|   | 8.3  |                                | 116               |

|   |      |                                |                   |

|   | 8.4  | 1                              | 120               |

|   |      |                                | 121               |

|   | ~ ~  |                                | 121               |

|   | 8.5  | Conclusion                     | 122               |

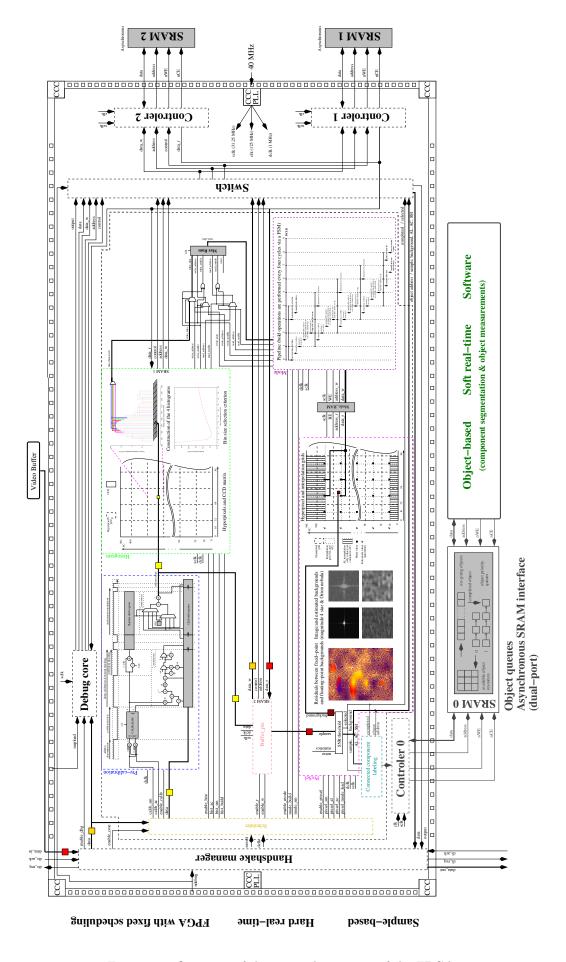

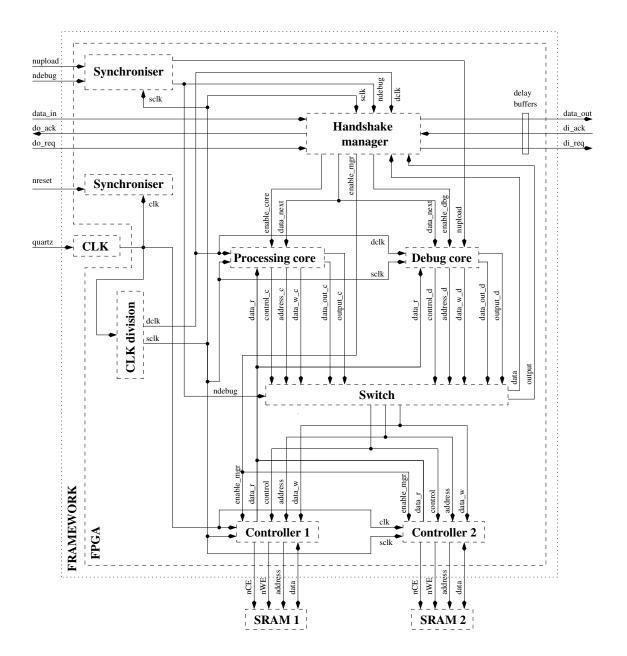

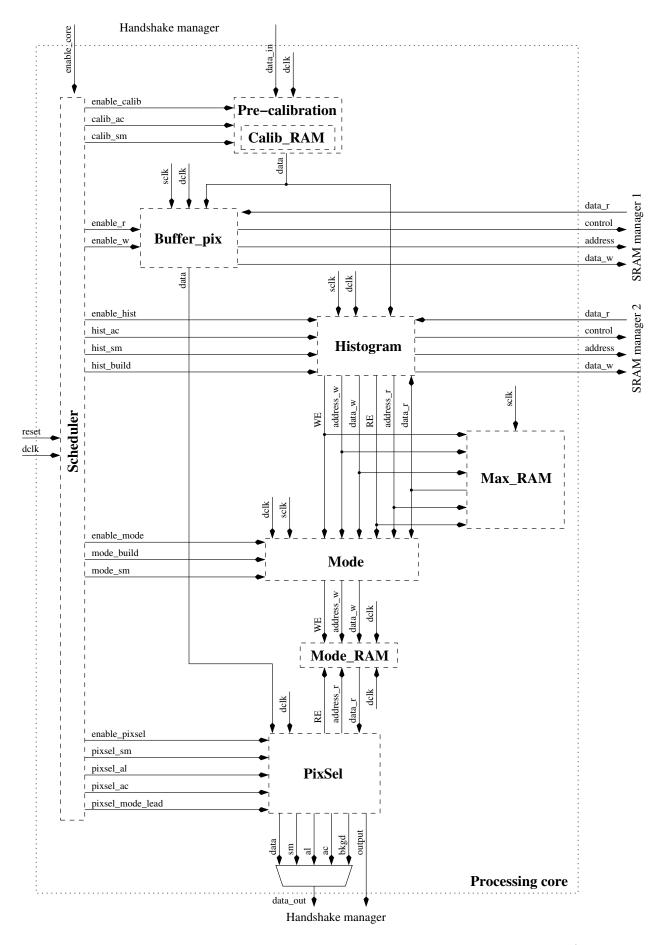

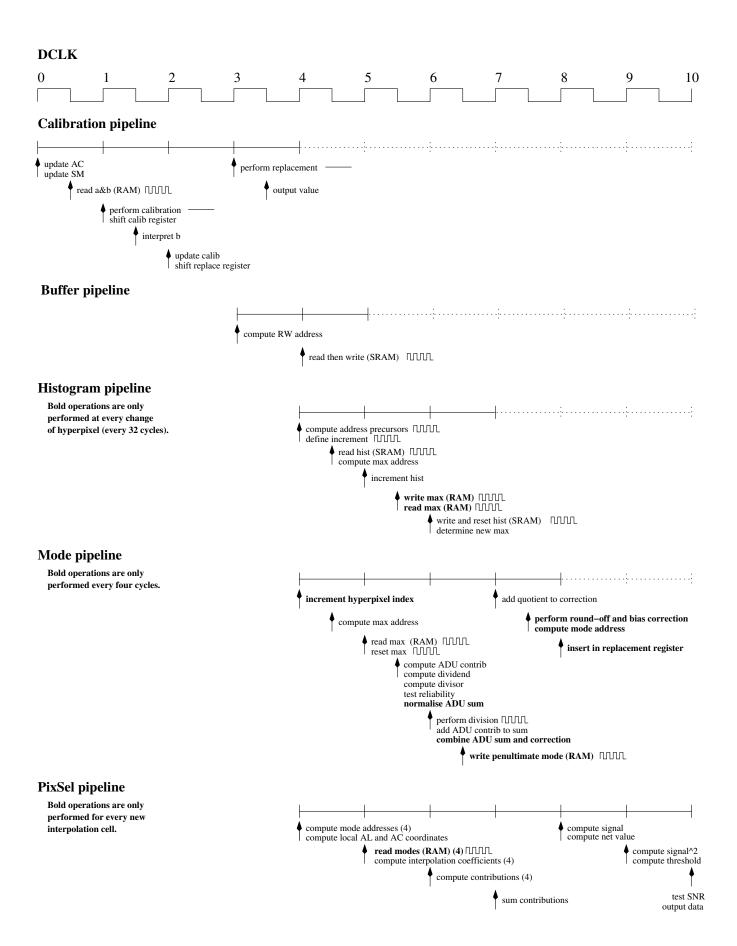

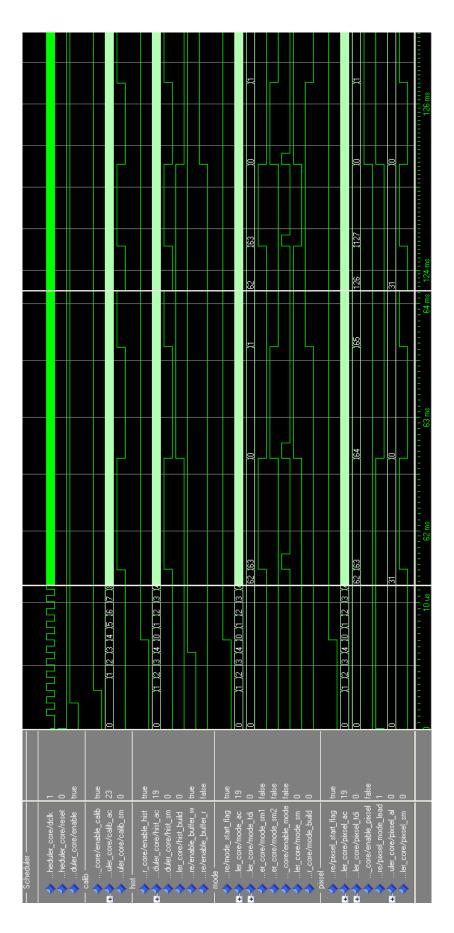

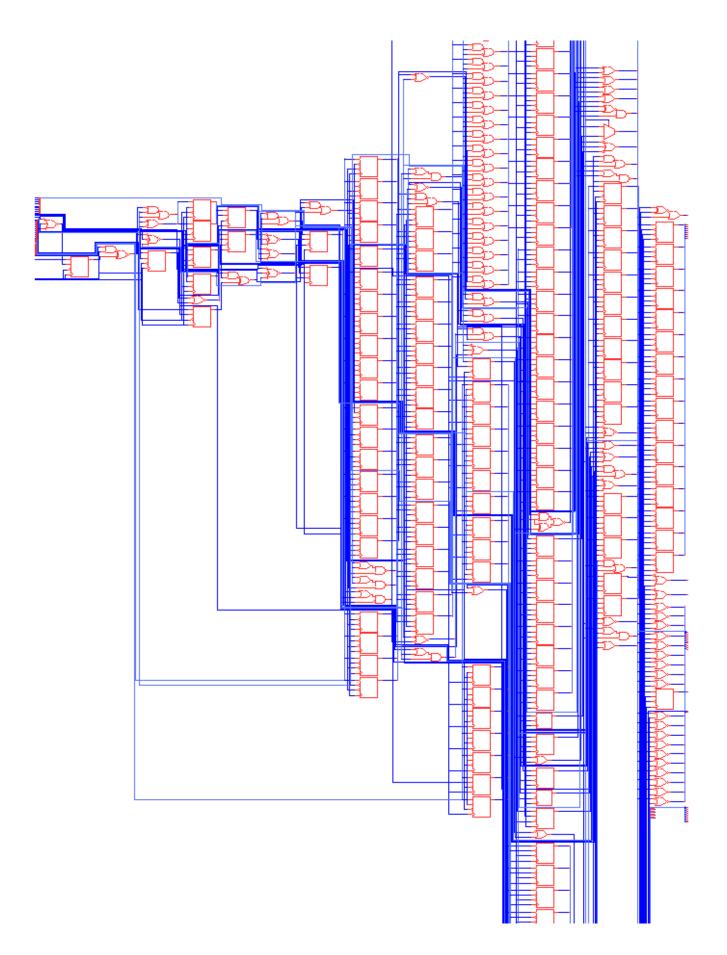

| 9 | Inte | ernal architecture of the FPGA | 123               |

|   | 9.1  | Introduction                   | 123               |

|   | 9.2  |                                | 124               |

|   |      |                                | 124               |

|   |      | •                              | 125               |

|   |      |                                | 125               |

|   |      |                                | $\frac{120}{129}$ |

|   |      | 1                              | _                 |

|   | 0.0  |                                | 131               |

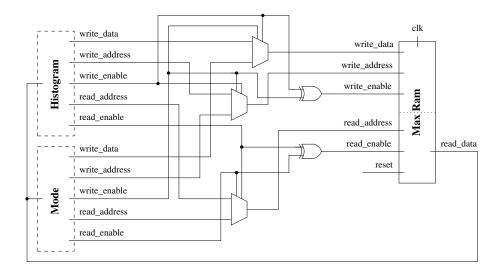

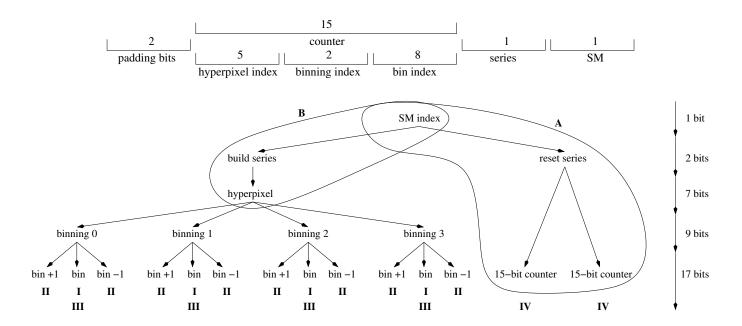

|   | 9.3  |                                | 132               |

|   |      | 1                              | 132               |

|   |      | 1                              | 132               |

|   |      | v                              | 133               |

|   |      | •                              | 135               |

|   | 9.4  | Reset policy                   | 140               |

|   |      | 9.4.1 Introduction             | 140               |

|   |      | 9.4.2 Implementation           | 141               |

|   | 9.5  | Clocks                         | 142               |

|   |      | 9.5.1 Functional               | 142               |

|   |      |                                | 143               |

|   |      | •                              | 144               |

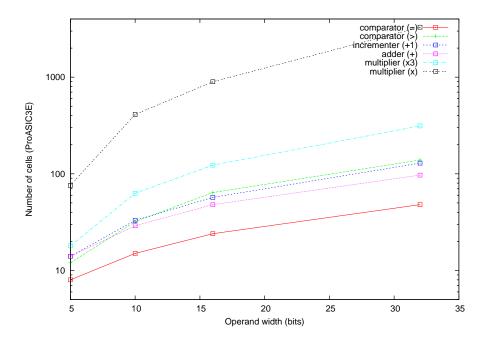

|   | 9.6  |                                | 145               |

|   | 0.0  |                                | 145               |

|   |      |                                | 146               |

|   |      |                                | 140               |

|   | 0.7  | •                              |                   |

|   | 9.7  | Conclusion                     | 147               |

vi CONTENTS

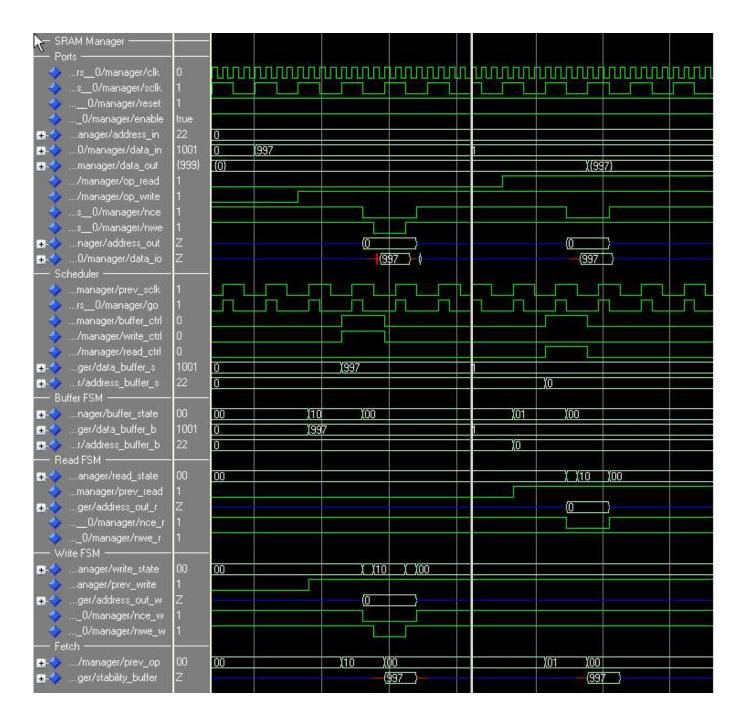

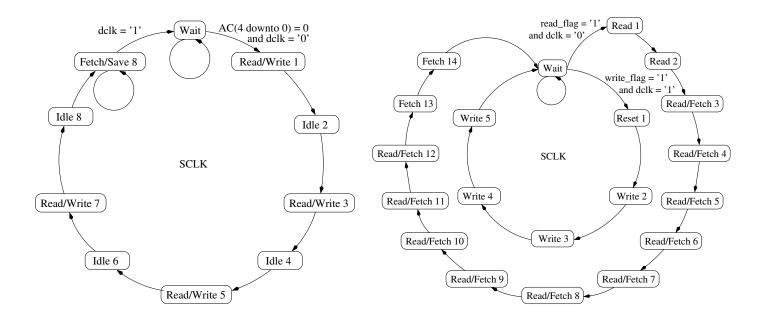

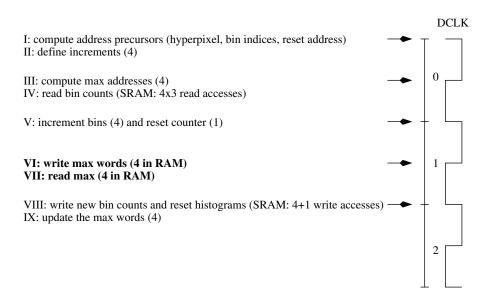

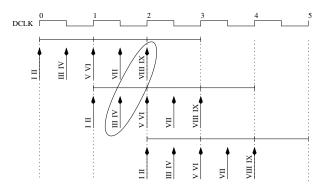

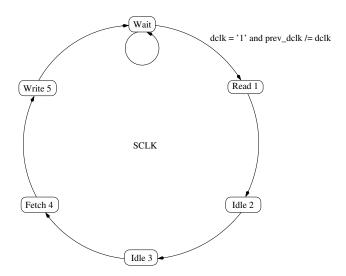

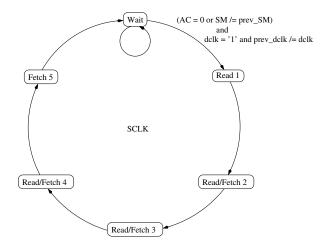

| 10 | Δ s <sub>371</sub> | nchronous SRAM controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 149               |

|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 10 |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 149               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

|    |                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 150               |

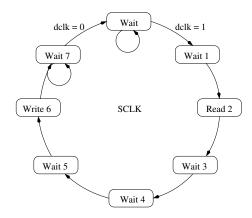

|    | 10.3               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 151               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 151               |

|    |                    | 10.3.2 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 154               |

|    |                    | 10.3.3 General considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 154               |

|    | 10.4               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 155               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 155               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 156               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 157               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 158               |

|    |                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 158               |

|    | 10.5               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 159               |

|    |                    | 10.5.1 Performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 159               |

|    | 10.6               | SRAM VHDL model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 160               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163               |

|    | -                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| 11 | Fixe               | ed-point formulae                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 165               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 165               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 166               |

|    | 11.4               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 166               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 168               |

|    | 11.3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 170               |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 171               |

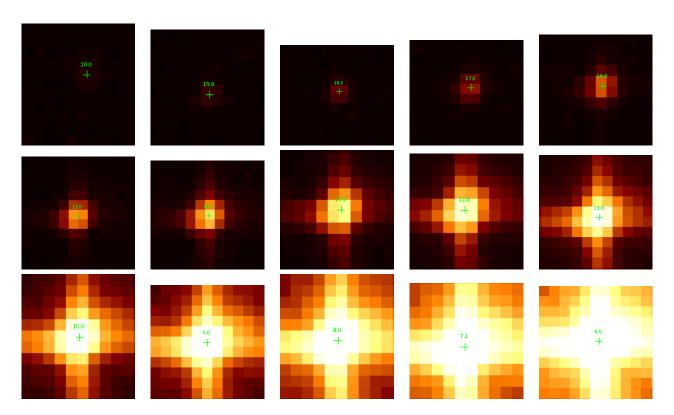

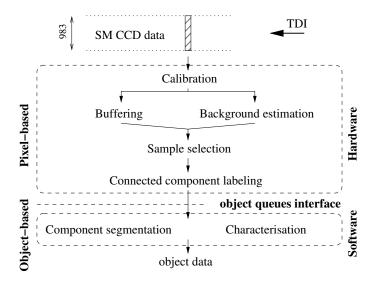

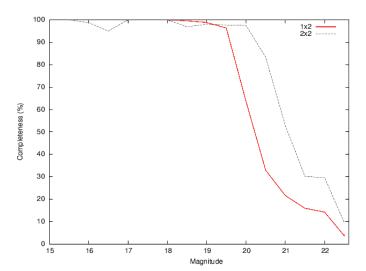

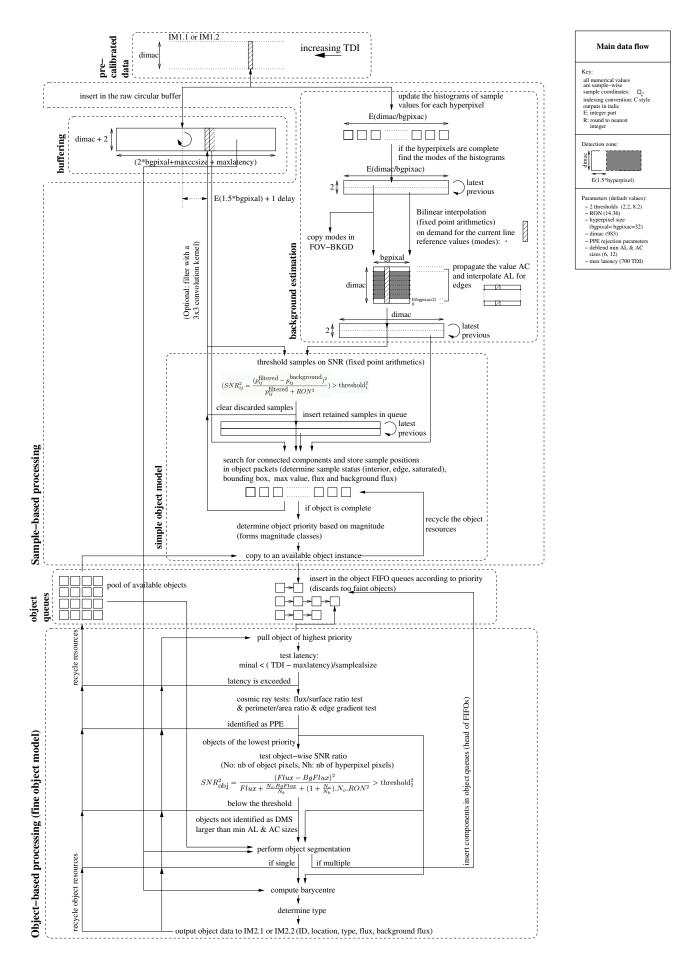

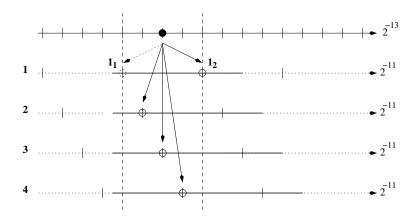

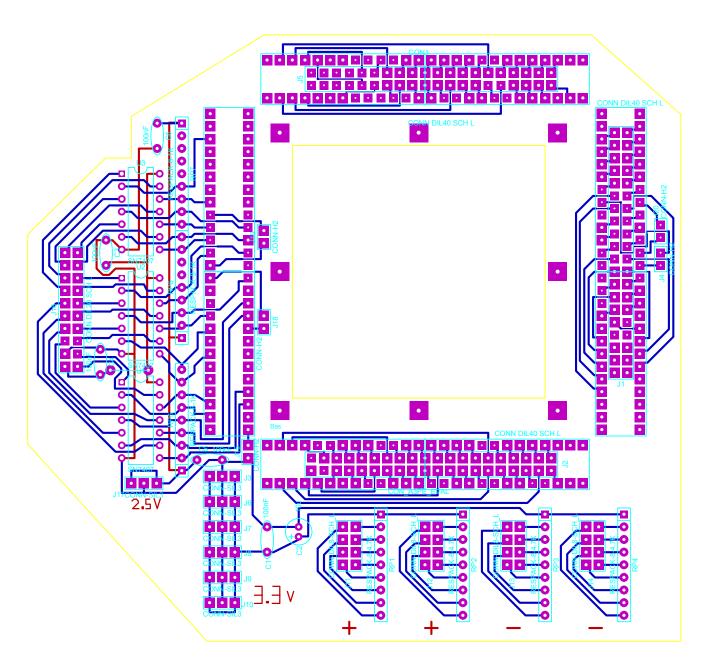

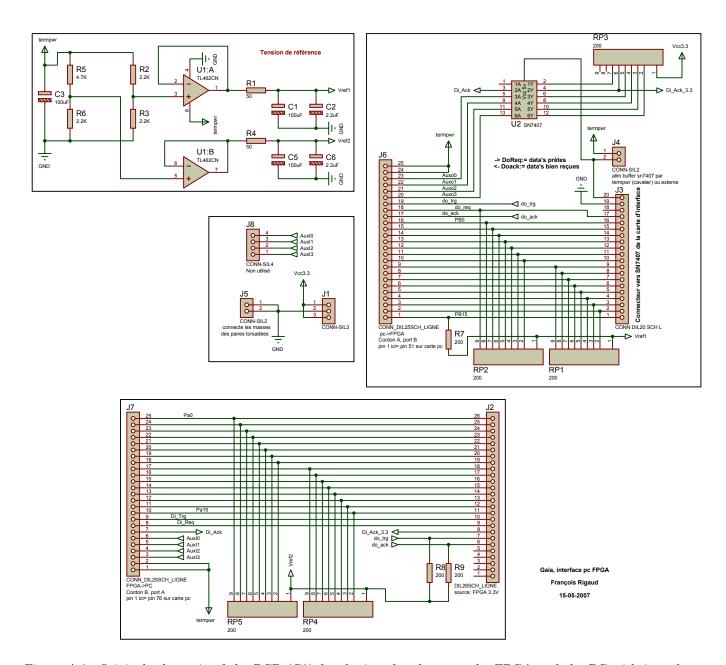

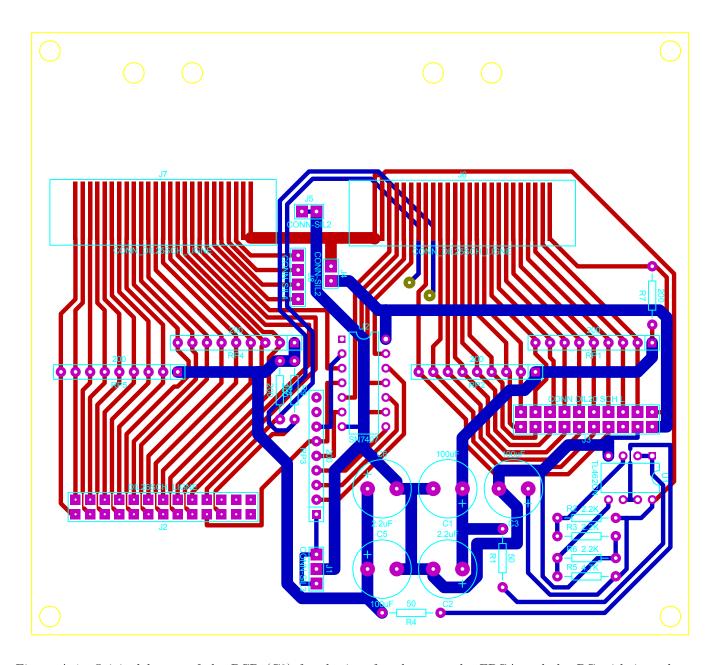

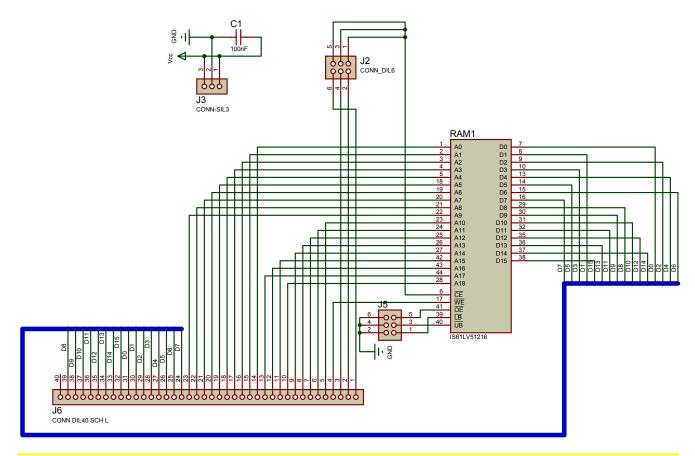

|    |                    | 11.3.2 Mode determination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 176               |